# **FPGA Basics 3** Sequential Logic Design and Simulation **GNSS** Receiver Architecture **FPGA** Antenna IF signal Micro-Correlators Controller Position Frontend Velocity Acquisition Timing Tracking Navigation Channel **RF** Signal **Digital Signal**

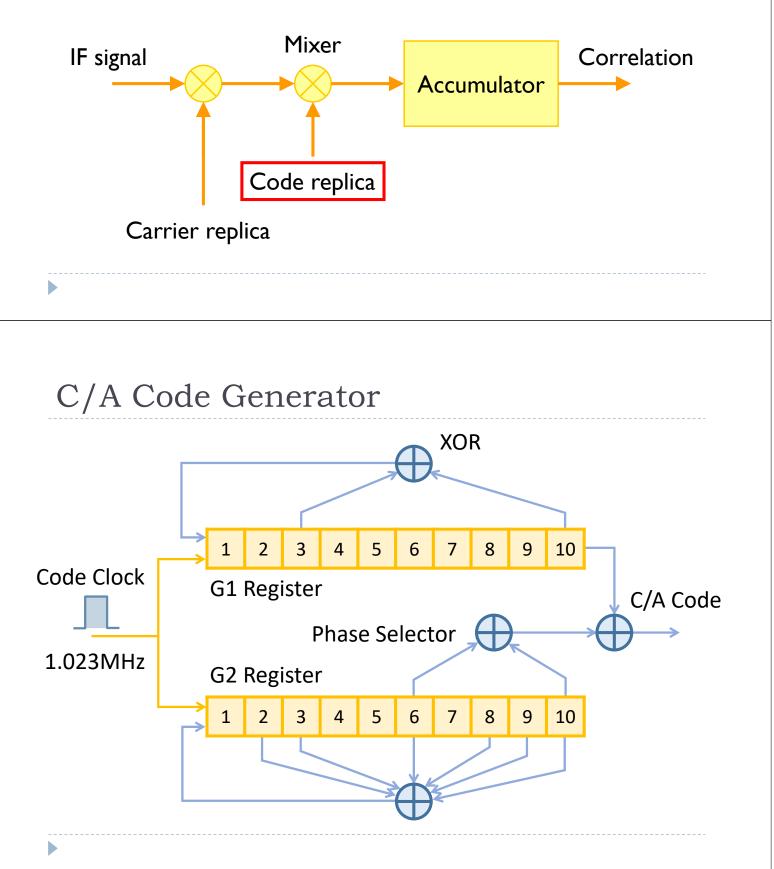

# **GNSS** Correlator Architecture

- Correlators are the key operation for GNSS receivers to synchronize with the incoming signal.

- The maximum correlation peak is acquired when the both code and carrier replicas match the incoming signal.

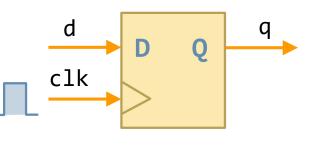

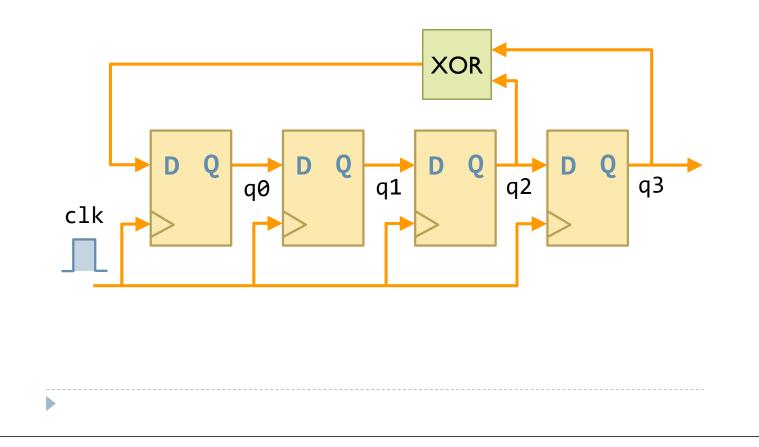

# Maximum Length Sequence

- A maximum length sequence, also sometimes called an <u>m-</u> <u>sequence</u>, is a type of pseudorandom binary sequence.

- They are bit sequences generated using maximal linearfeedback shift registers.

- They are periodic and reproduce every binary sequence, except the zero vector.

- For length-*m* registers, they produce a sequence of length  $2^m 1$ .

# Sequential Logic in Verilog

- Sequential logic defines modules that have memory.

- Flip-Flops, Latches, Registers, Finite State Machines, ...

- Sequential logic is triggered by a "clock" event.

- Flip-Flops are sensitive to the transitioning (edge) of clock.

- Latches are sensitive to level of the signal

- Combinational constructors are not sufficient.

- We need new constructor: always

- Whenever the event in the sensitivity list occurs, the statement is executed.

# always @ (sensitivity list) statement;

Þ

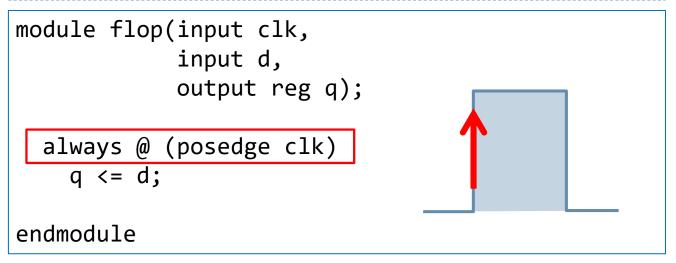

# D Flip-Flop

always @ (posedge clk) q <= d;

endmodule

## D Flip-Flop

- The posedge defines a rising edge.

- The process will trigger only if the clk signal rises.

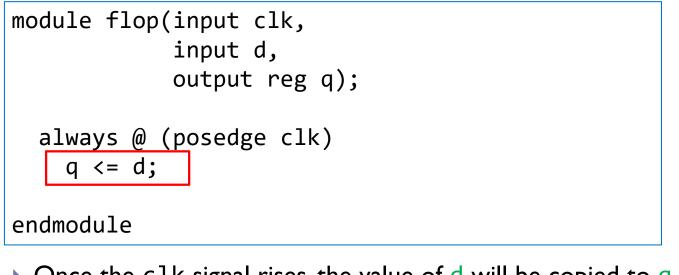

# D Flip-Flop

- Once the clk signal rises, the value of d will be copied to q.

- "assign" statement is <u>not</u> used within always block.

- The "<=" describes a "non-blocking" assignment.</p>

- Assigned variables need to be declared as reg.

- The name reg does not necessarily mean that the value is a register.

Þ

## D Flip-Flop with Synchronous Reset

always @ (posedge clk) begin

if (!rstn) q <= 0;

else q <= d;

end</pre>

endmodule

Reset only happens when the clock rises.

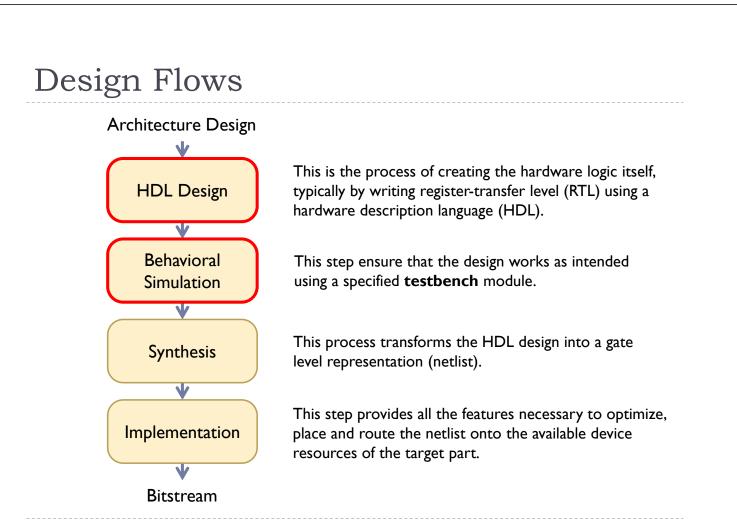

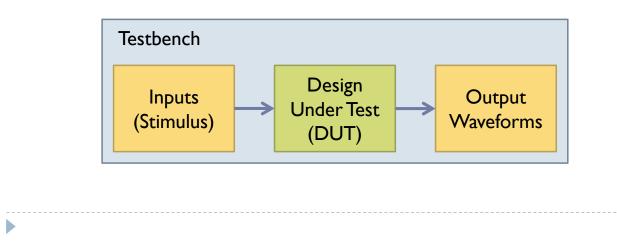

## What is a Testbench?

- Testbenches consist of non-synthesizable Verilog code which generates inputs to the design and checks that the outputs are correct.

- The diagram below shows the typical architecture of a simple testbench.

#### Simulation Tools

- The stimulus block generates the inputs to the FPGA design under test, and the output block shows the output waveforms to ensure they have the correct values.

- Many freely available software packages offer behavioral simulation capability.

- Commercial: <u>Vivado</u> (AMD/Xilinx) and Quartus (Intel)

- Open Source: Icarus Verilog and GTKWave

- Online: EDA Playground (https://www.edaplayground.com/)

#### Linear Feedback Shift Register (LFSR)

#### Linear Feedback Shift Register (LFSR)

| q3 | q2 | ٩l | <b>q0</b> | Decimal | Hex |

|----|----|----|-----------|---------|-----|

| 0  | 0  | 0  | I         | I       | I   |

| 0  | 0  | I  | 0         | 2       | 2   |

| 0  | I  | 0  | 0         | 4       | 4   |

| I  | 0  | 0  | I         | 9       | 9   |

| 0  | 0  | I  | I         | 3       | 3   |

| 0  | I  | I  | 0         | 6       | 6   |

| I  | I  | 0  | I         | 13      | d   |

| I  | 0  | I  | 0         | 10      | а   |

| 0  | I  | 0  | I         | 5       | 5   |

| I  | 0  | I  | I         | П       | b   |

| 0  | I  | I  | I         | 7       | 7   |

| I  | I  | I  | I         | 15      | f   |

| I  | Ι  | I  | 0         | 14      | е   |

| I  | I  | 0  | 0         | 12      | с   |

| Ι  | 0  | 0  | 0         | 8       | 8   |

| 0  | 0  | 0  | I         | I       | I   |

#### LFSR Verilog Example

endmodule

#### Testbench

#### lfsr\_tb.v

```

module lfsr_tb;

```

```

reg clk;

reg rstn;

wire [3:0] q;

```

```

lfsr dut(clk, rstn, q);

```

```

always #5 clk <= ~clk;</pre>

```

#### Continued...

#### Testbench

```

initial begin

clk <= 0;

rstn <= 0;

#20 rstn <= 1;

#80 rstn <= 0;

#50 rstn <= 0;

#200 $finish;

end

endmodule</pre>

```